W956D6HB

64Mb Async./Burst/Sync./A/D MUX

1. GENERAL DESCRIPTION

Winbond x16 ADMUX products are high-speed, CMOS pseudo-static random access memory developed for lowpower, portable applications. The device has a DRAM core organized. These devices are a variation of the industrystandard Flash control interface, with a multiplexed address/data bus. The multiplexed address and data functionality

dramatically reduce the required signal count, and increase READ/WRITE bandwidth.

For seamless operation on a burst Flash bus, Winbond x16 ADMUX products incorporate a transparent self-refresh

mechanism. The hidden refresh requires no additional support from the system memory controller and has no

significant impact on device READ/WRITE performance.

Two user-accessible control registers define device operation. The bus configuration register (BCR) defines how the

Winbond x16 ADMUX device interacts with the system memory bus and is nearly identical to its counterpart on burst

mode Flash devices. The refresh configuration register (RCR) is used to control how refresh is performed on the

DRAM array. These registers are automatically loaded with default settings during power-up and can be updated

anytime during normal operation.

Special attention has been focused on standby current consumption during self refresh. Winbond x16 ADMUX

products include two mechanisms to minimize standby current. Partial-array refresh (PAR) enables the system to limit

refresh to only that part of the DRAM array that contains essential data. Temperature-compensated refresh (TCR)

uses an on-chip sensor to adjust the refresh rate to match the device temperature—the refresh rate decreases at

lower temperatures to minimize current consumption during standby. The system-configurable refresh mechanisms

are accessed through the RCR.

Winbond x16 ADMUX is compliant with the industry-standard CellularRAM 1.5 x16 A/D MUX.

2. FEATURES

•Supports asynchronous and burst operations

• VCC, VCCQ Voltages:

1.7V–1.95V VCC

1.7V–1.95V VCCQ

• Random access time: 70ns

• Burst mode READ and WRITE access:

4, 8, 16, or 32 words, or continuous burst

Burst wrap or sequential

Max clock rate: 133 MHz (tCLK = 7.5ns)

• Low power consumption:

Asynchronous READ: 20ns.

4. CE# must go HIGH before any clock edge following the last word of a defined-length burst.

- 48 -

Publication Release Date : May 29,2013

Revision : A01-003

�W956D6HB

64Mb Async./Burst/Sync./A/D MUX

10.2.14 Burst WRITE Terminate at End of Row (Wrap Off)

CLK

VIH

VIL

tCLK

VIH

A [max:16 ]

VIL

ADV #

VIH

VIL

VIH

LB # /UB #

VIL

WE #

VIH

VIL

OE# VIH

VIL

CE #

tcsp

tHD

VIH

Note 2

VIL

t SP t HD

VIH

A/DQ[15:0 ]

VIL

Valid input Valid input Valid input

END OF ROW

tHZ

WAIT

t HZ

VOH

VOL

High - Z

tKOH

tKHTL

Don' t Care

Undefined

Notes: 1. Non-default BCR settings for burst WRITE at end of row: fixed or variable latency, WAIT active LOW, WAIT asserted

during delay (shown as solid line).

2. For burst WRITEs, CE# must go HIGH before the second CLK after the WAIT period begins (before the second CLK after

WAIT asserts with BCR[8] = 0, or before the third CLK after WAIT asserts with BCR[8] = 1).

- 49 -

Publication Release Date : May 29,2013

Revision : A01-003

�W956D6HB

64Mb Async./Burst/Sync./A/D MUX

10.2.15 Burst WRITE Row Boundary Crossing

VIH

VIL

CLK

t CLK

A[max:16]

VIH

VIL

ADV #

VIH

VIL

LB# / UB #

VIH

VIL

WE #

OE#

VIH

VIL

VIH

VIL

VIH

CE#

V IL

VIH

A/DQ[15:0]

VIL

WAIT

t SP t HD

Valid input

End of row

Valid input Valid input

Valid input Valid input

t KHTL

VOH

t KHTL

V OL

t KOH

Note 2

t KOH

Don' t Care

Undefined

Notes: 1. Non-default BCR settings for burst WRITE at end of row: fixed or variable latency, WAIT active LOW, WAIT asserted

during delay (shown as solid line).

2. WAIT will be asserted for LC cycles for variable latency, or LC cycles for fixed latency.

- 50 -

Publication Release Date : May 29,2013

Revision : A01-003

�W956D6HB

64Mb Async./Burst/Sync./A/D MUX

10.2.16 Burst WRITE Followed by Burst READ

VIH

CLK VIL

A[max:16] VIH

VIL

VIH

ADV# VIL

tCLK

tSP tHD

tSP tHD

Valid

Valid

Valid

Address

Address

Address

tSP tHD

tSP

LB#/UB# VIH

VIL

tHD t CBPH

Note 2

OE # VIH

VIL

VIH

WE# VIL

tHD

tCSP

VIH

CE# VIL

tSP

tSP

tHD

A/DQ[15:0] VIH

Valid

Address

IN/OUT VIL

VOH High-Z t HD

WAIT VOL

tHD

tSP

t CSP

tOHZ

tSP tHD

tSP tHD t BOE

t SP tHD

D0 D1 D2 D3

Valid

address

VOH

VOL

tACLK

tKOH

Valid

Output

Valid

Output

Valid

Output

Valid

Output

High- Z

Don' t Care Undefined

Notes: 1. Non-default BCR settings for burst WRITE followed by burst READ: fixed or variable latency, latency code 2 (3 clocks),

WAIT active LOW, WAIT asserted during delay.

2. A refresh opportunity must be provided every tCEM. A refresh opportunity is satisfied by either of the following

two conditions: a) clocked CE# HIGH, or b) CE# HIGH for longer than 15ns.

- 51 -

Publication Release Date : May 29,2013

Revision : A01-003

�W956D6HB

64Mb Async./Burst/Sync./A/D MUX

10.2.17 Asynchronous WRITE Followed by Burst READ

CLK

A[max:16]

tCLK

VIH

VIL

VIH

VIL

ADV#

VIH

VIL

LB #/ UB #

VIH

VIL

CE #

VIH

VIL

t SP

Valid address

t AVS

t AS

t AS

t HD

Valid address

t AVH

t SP tHD

t VP

tBW

t HD

tSP

tCBPH

tCW

tCSP

tOHZ

Note 2

OE #

VIH

VIL

WE #

VIH

VIL

A/DQ[15:0]

VIH

VIL

tWC

t WP

t AS

VOH

VOL

t SP tHD

Valid address

t AVS

WAIT

t SP tHD

tAVH

Data

tDW tDH

VOH

VOL

tKHTL

tBOE

Valid

output

Valid

address

t ACLK

Valid

output

Valid

output

t KOH

Valid

output

High- Z

Don't Care

Undefined

Notes: 1. Non-default BCR settings for asynchronous WRITE, with ADV# LOW, followed by burst READ: fixed or variable latency,

latency code 2 (3 clocks), WAIT active LOW, WAIT asserted during delay.

2. When the device is transitioning between asynchronous and variable-latency burst operations, CE# must go HIGH. CE#

can stay LOW when the device is transitioning to fixed-latency burst READs. A refresh opportunity must be provided every

tCEM. A refresh opportunity is satisfied by either of the following two conditions: a) clocked CE# HIGH, or b) CE# HIGH for

longer than 15ns.

- 52 -

Publication Release Date : May 29,2013

Revision : A01-003

�W956D6HB

64Mb Async./Burst/Sync./A/D MUX

10.2.18 Burst READ Followed by Asynchronous WRITE

tCLK

CLK

V IH

VIL

V IH

A[max: 16 ]

VIL

V IH

ADV #

VIL

tSP t HD

Vaild address

Valid address

t AVS

tAVH

t AS

tSP t HD

CE #

V IH

VIL

OE #

V IH

VIL

WE #

V IH

VIL

WAIT

VOH

VOL

tVP

t CW

Note 2

t BOE

tSP tHD

tSP

High-Z

t WP

VOH

VOL

t WPH

t BW

tHD

t SP tHD

Valid address

t OHZ

tOLZ

V IH

LB#/ UB#

VIL

V IH

A/DQ [15:0]

VIL

tCBPH

t HZ t AS

tHD

t CSP

t AW

t VS

t ACLK tKOH

Valid output

tKOH

t AS

VIH

VI L

t AVS tAVH

Valid address

tDW

tDH

Valid Input

High - Z

tKHTL

READ Burst Identified

( WE # = HIGH )

t KHTL

Don' t Care

Undefined

Notes: 1.Non-default BCR settings for burst READ followed by asynchronous WRITE using ADV#: fixed or variable latency, latency

code 2 (3 clocks), WAIT active LOW, WAIT asserted during delay.

2.When the device is transitioning between asynchronous and variable-latency burst operations, CE# must go HIGH. CE#

can stay LOW when the device is transitioning from fixed-latency burst READs; asynchronous operation begins at the

falling edge of ADV#. A refresh opportunity must be provided every tCEM. A refresh opportunity is satisfied by either of the

following two conditions: a) clocked CE# HIGH, or b) CE# HIGH for longer than 15ns.

- 53 -

Publication Release Date : May 29,2013

Revision : A01-003

�W956D6HB

64Mb Async./Burst/Sync./A/D MUX

10.2.19 Asynchronous WRITE Followed by Asynchronous READ

VIH

A[max:16]

VIL

VIH

ADV#

VIL

Valid address

t AVS

t AVH

t AS

t AW

tVP

VIH

WE#

t AVH

tVP

tBHZ

tCVS

t BW

t BA

tCPH

t CVS

t AA

t AADV

t WR

t VS

t HZ

t CO

t CW

Note 1

VIL

OE#

tOLZ

t OE

VIH

VIL

VIL

VOH

tOHZ

tWP

VIH

VIH

A/DQ[15:0]

VIL

WAIT

t AVS

tAS

VIH

LB#/UB#

VIL

CE#

Valid address

t AS

Valid address

t AVS

Valid input

t AVH

tDS

Data Valid address

tAVS t AVH

t DH

VOH

Valid Output

VOL

t AA

tOEW

t AW

tHZ

High - Z

VOL

Don't Care

Undefined

Notes: 1.When configured for synchronous mode (BCR[15] = 0), CE# must remain HIGH for at least 5ns (tCPH) to schedule the

appropriate refresh interval. Otherwise, tCPH is only required after CE#-controlled WRITEs.

- 54 -

Publication Release Date : May 29,2013

Revision : A01-003

�W956D6HB

64Mb Async./Burst/Sync./A/D MUX

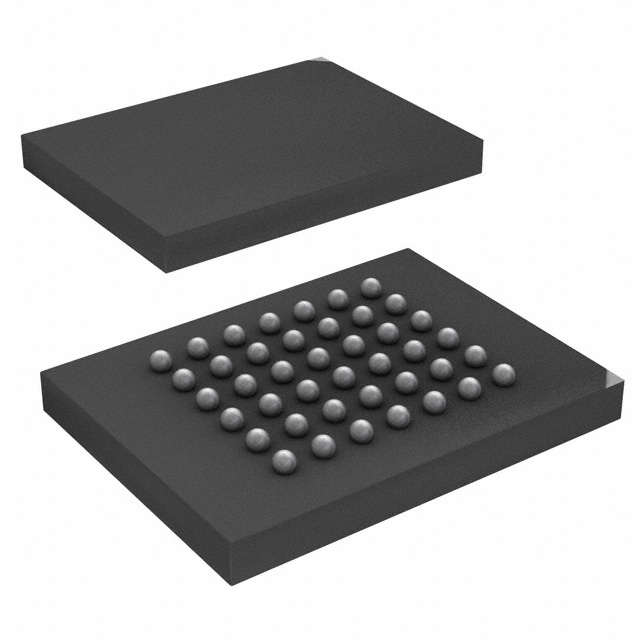

11. PACKAGE DESCRIPTION

11.1 Package Dimension

VFBGA 54BALL (6X8 mm^2,Ball pitch:0.75mm, Ø =0.4mm)

Note:

1. Ball land:0.45mm. Ball opening:0.35mm.

PCB ball land suggested

很抱歉,暂时无法提供与“W956D6HBCX7I TR”相匹配的价格&库存,您可以联系我们找货

免费人工找货